# AM-IP4k

## Datasheet

Version: Date: 1.3 05/02/2020

AMAC ASIC- Mikrosensoranwendung Chemnitz GmbH Kopernikusstr. 16 D-09117 Chemnitz Germany

## **Revision History**

| Date       | Revision | Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/03/2018 | 1.0      | First Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 07/07/2018 | 1.1      | At 2 Features Analogue input range 220 kHZ<br>Figure 1 Block diagram ink word changed to inc.<br>Figure 2 Functional block diagram ink word changed to inc.<br>Overview. Switching analogue filter deleted and modified to low-pass.<br>Figure 4 Input signals (single-ended) update. U to V.<br>Figure 5 Input signals differential update. U to V.<br>Figure 11 Reference signal MVAL(ZMODE) updated to CFG3/ZMODE 01<br>Figure 21 Mnimum circuit of the AM-IP4K added<br>Table 1: Pin assignment AM-IP4k QFN56 Pin assignment, revised<br>Instrument amplifier changed to instrumentation amplifiers<br>7.2.2 Phase adjustment added<br>Formula 1 phase adjustment added<br>Formula 2 added<br>Table 5 configuration options<br>CFG2/IRDIV2 added at Interpolation rate.<br>corrected: CFG4/ZPOS2, CFG2/TRGSLP, CFG2/TEAN<br>CFG3 / PHRENA added at phase correction<br>CFGS3 / PHRENA added at phase correction<br>CFGS3 / PHRENA added at phase correction<br>CFGS3 / SI20 corrected<br>Table 6 at CFG2/TEAN corrected<br>Table 11: Register "Correction"<br>DISKSC 0x013 [1] changed to 0x013 [2] and 0x09[9] changed to 0x09[10]<br>DISKSC 0x013 [2] changed to 0x013 [2] and 0x09[9] changed to 0x09[9]<br>7.4.1 Interpolation rate. Basic interpolation rates described.<br>7.6 In text 6 possibilities corrected to 7 possibilities<br>At 7.6.1 Sources of error. Correction error see chapter 7.5 changed to 7.7.4<br>At 7.8 Measured Trigger value<br>Timer high range changed from 22 <sup>24</sup> /f <sub>osz</sub> to 22 <sup>16</sup> /f <sub>osz</sub><br>Table 18: ABZ modes (Register CFG1) modified mode 110 deleted.<br>Table 20: Sensor adjustment at Phase adjustment, activate controller corrected.<br>Figure for Duty Cycle = 50 and PHI = 45<br>Register CFG3 DISZ reset value changed to 0<br>Register CFG3 IDSZ reset value changed to 0<br>Register CFG3 IDSZ reset value changed to 0<br>Register CFG3 DISZ reset value changed to 0<br>Register CFG3 DISZ reset value changed to 0<br>Register CFG3 IDSZ reset value changed to 0<br>Register CFG3 IDSZ reset value changed to 0<br>Register CFG3 DISZ reset value changed to 0<br>Register CFG3 DISZ reset value changed to 0<br>Register CFG3 DISZ reset value changed |

| 15/01/2020 | 1.2      | Deleted error from non-existing reference. Page 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 05/02/2020 | 1.3      | Table 18: ABZ modes (Register CFG1) modified, mode 110 deleted.<br>At Features Basis Interpolation rate 2560 added.<br>At Register CGFG2 TEAN to TEAEN changed.<br>Pin assignment V1P1, VRH, VRM, and VRL as AO corrected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### © Copyright 2020 AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH

Subject to change without prior notice.

Our policy is one of continuous improvement, and consequently the equipment may vary slightly from the description and specifications in this publication. The specifications, illustrations and descriptions provided in this documentation are not binding in detail. No part of this publication may be reproduced in any form, or by any means, without the prior written permission of AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH. All rights according to the law on copyright remain expressly reserved to AMAC ASIC- und Mikrosensoranwendung Chemnitz GmbH.

## Table of contents

|    | Overview                                                                    |      |

|----|-----------------------------------------------------------------------------|------|

| 2  | Features                                                                    | 7    |

| 3  | Ordering information                                                        | 7    |

| 4  | Application overview                                                        | 8    |

| 5  | Pin assignment                                                              | 9    |

|    | 5.1 Package                                                                 | 10   |

| 6  | Startup behaviour / Configuration options                                   | . 11 |

|    | 6.1 Reset                                                                   |      |

|    | 6.2 Configuration                                                           | . 11 |

| 7  | Functional description                                                      | .13  |

|    | 7.1 Input amplifier / Low-pass filter                                       | .13  |

|    | 7.2 Signal adjustment                                                       | 14   |

|    | 7.2.1 Amplitude and offset                                                  | 14   |

|    | 7.2.2 Phase Adjustment                                                      | 15   |

|    | 7.3 Signal correction (Periodic errors)                                     | 15   |

|    | 7.4 Interpolation                                                           | 17   |

|    | 7.4.1 Interpolation rate                                                    | 17   |

|    | 7.4.2 Edge separation control / Interval time t <sub>pp</sub> / Hysteresis  | .18  |

|    | 7.4.3 Index signal Z                                                        | .18  |

|    | 7.5 Mode / Maximum input frequency                                          | .19  |

|    | 7.6 Sensor monitoring.                                                      | 20   |

|    | 7.6.1 Sources of error                                                      | .21  |

|    | 7.7 Outputs ABZ                                                             |      |

|    | 7.7.1 Standard ABZ                                                          |      |

|    | 7.7.2 Controller / DSP                                                      |      |

|    | 7.7.3 Reference position adjustment                                         |      |

|    | 7.7.4 Sensor adjustment                                                     |      |

|    | 7.8 Measured value trigger                                                  |      |

|    | 7.9 Registers of measured values                                            | 27   |

|    | 7.10 Counter preset / SPI commands / Control signals<br>Digital interfaces. | .28  |

| 8  | Digital interfaces                                                          | 29   |

|    | 8.1 Serial interface SPI                                                    | .29  |

|    | 8.1.1 Signals                                                               |      |

|    | 8.1.2 Protocol                                                              |      |

|    | 8.1.3 Register access                                                       |      |

|    | 8.1.4 SPI – Synchronous / Asynchronous                                      | .30  |

|    | 8.2 SSI interface                                                           | 31   |

|    | 8.3 EEPROM                                                                  |      |

|    | Register                                                                    |      |

|    | Characteristic values                                                       |      |

| 11 | Application note                                                            |      |

|    | 11.1 Circuitry                                                              | 47   |

|    | 11.2 Connecting different types of sensors                                  | 50   |

|    | 11.3 EEPROM                                                                 |      |

| N  | otes                                                                        | 54   |

## List of figures

| Figure 1: Block diagram                                          | 6  |

|------------------------------------------------------------------|----|

| Figure 2: Functional block diagram                               |    |

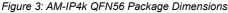

| Figure 3: AM-IP4k QFN56 Package Dimensions                       |    |

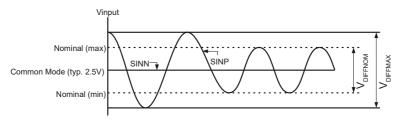

| Figure 4: Input signals (single-ended)                           |    |

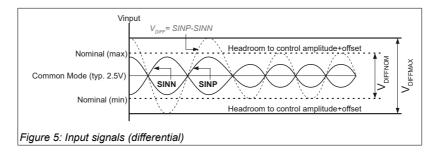

| Figure 5: Input signals (differential)                           |    |

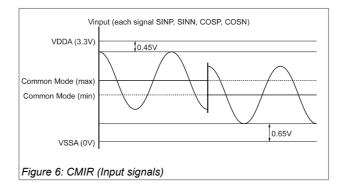

| Figure 6: CMIR (Input signals)                                   |    |

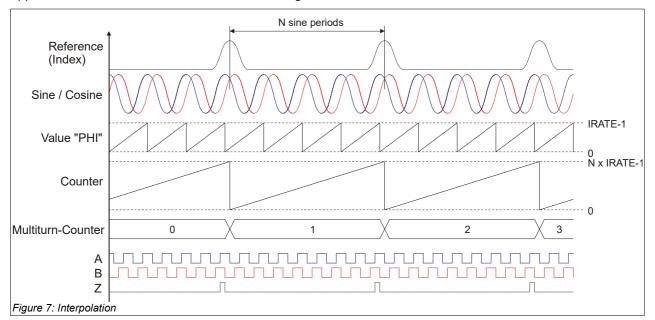

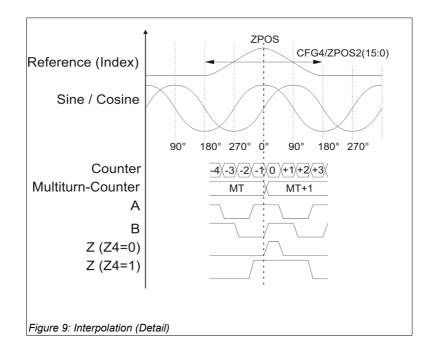

| Figure 7: Interpolation                                          |    |

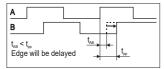

| Figure 8: Edge separation control Time discretisation Hysteresis |    |

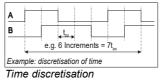

| Figure 9: Interpolation (Detail)                                 |    |

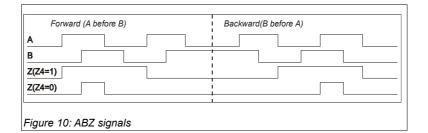

| Figure 10: ABZ signals                                           | 22 |

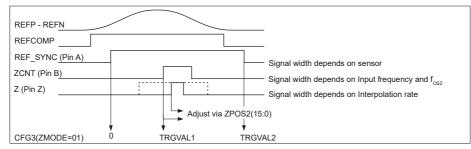

| Figure 11: Reference signal adjustment                           |    |

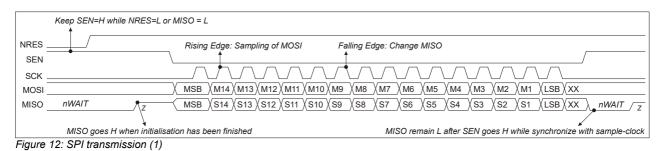

| Figure 12: SPI transmission (1)                                  | 29 |

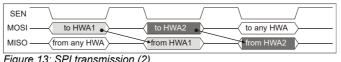

| Figure 13: SPI transmission (2)                                  |    |

| Figure 14: SPI write 8 bit                                       |    |

| Figure 15: SPI read 32 bit.                                      |    |

| Figure 16: SPI write 32 bit                                      |    |

| Figure 17: SPI read 3 x 32 bit.                                  |    |

| Figure 18: Initialisation of SSI hardware                        |    |

| Figure 19: SSI                                                   |    |

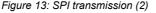

| Figure 20: SSI (Ring mode).                                      | 31 |

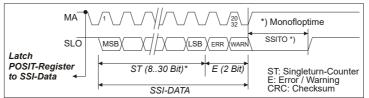

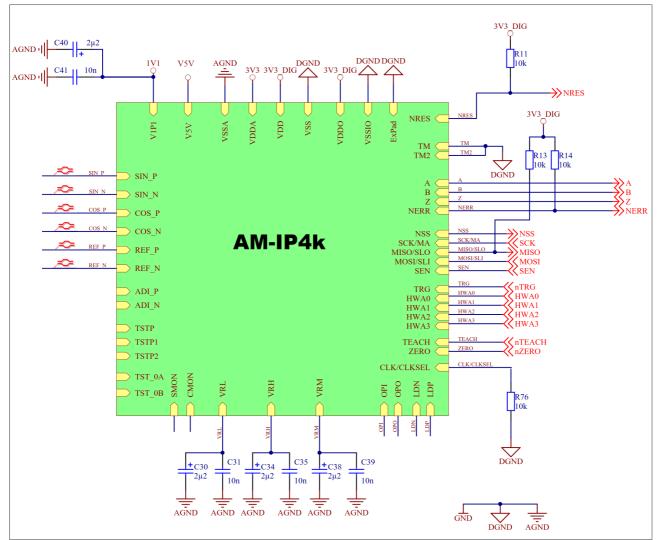

| Figure 21: Minimum circuit of the AM-IP4K.                       |    |

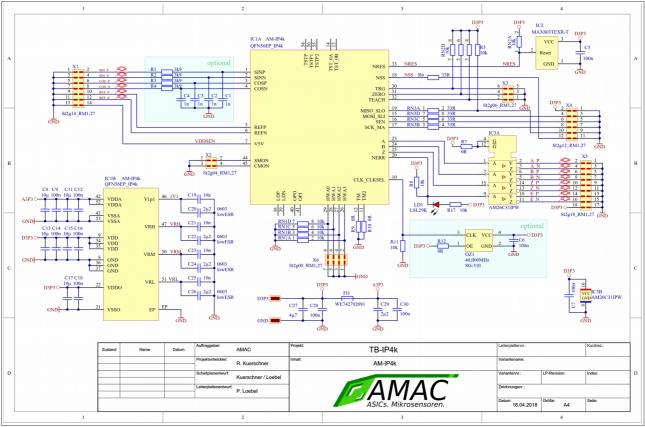

| Figure 22: AM-IP4k recommended circuit.                          |    |

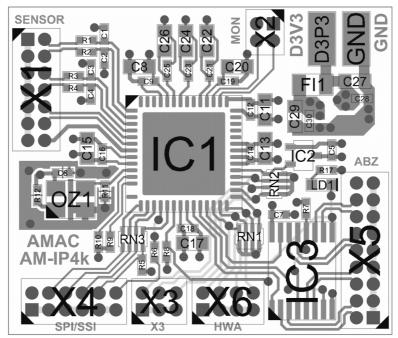

| Figure 23: AM-IP4k recommended PCB Layout                        |    |

| Figure 24: Sensor with differential output signals.              |    |

| Figure 25: Sensor with a nominal amplitude > 1Vpp                |    |

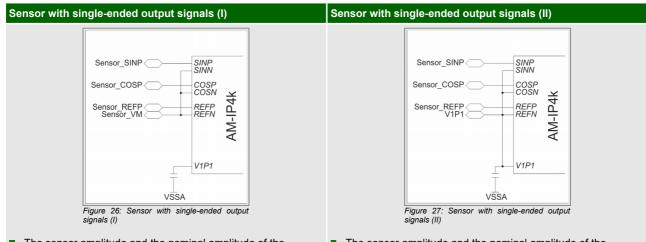

| Figure 26: Sensor with single-ended output signals (I).          |    |

| Figure 27: Sensor with single-ended output signals (II)          |    |

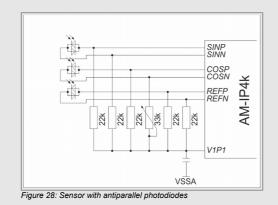

| Figure 28: Sensor with antiparallel photodiodes.                 |    |

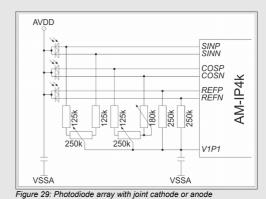

| Figure 29: Photodiode array with joint cathode or anode          | 51 |

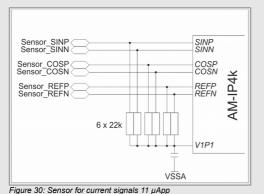

| Figure 30: Sensor for current signals 11 µApp                    |    |

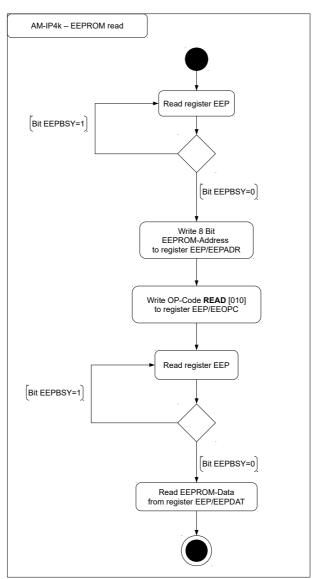

| Figure 31: Procedure sequence for EEPROM read                    |    |

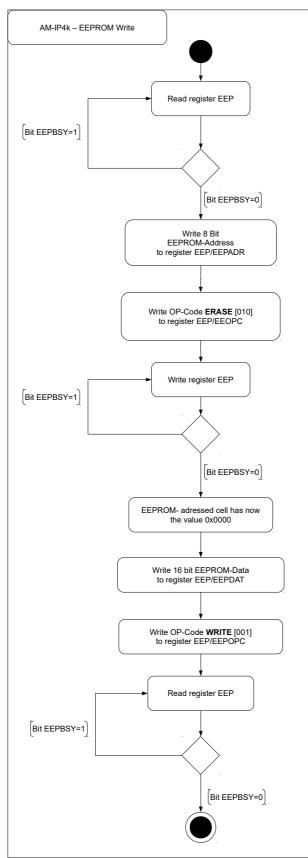

| Figure 32: Procedure sequence for EEPROM read                    | 53 |

## List of tables

| Table 1: Pin assignment QFN56                               | 9    |

|-------------------------------------------------------------|------|

| Table 2: Clock generator selection (Pin CLK_CLKSEL)         |      |

| Table 3: Serial interface selection AM-IP4k                 |      |

| Table 4: Switching of configuration source                  | . 11 |

| Table 5: Configuration options                              |      |

| Table 6: Default settings                                   |      |

| Table 7: Default interface settings                         |      |

| Table 8: Nominal amplitude configuration (Register CFG1)    | 13   |

| Table 9: Low-pass filter configuration (Register CFG2)      | 13   |

| Table 10: Example of common mode input voltage (CMIR)       | 14   |

| Table 11: Register "Correction"                             | 15   |

| Table 12: Control parameter of coefficient calculation      | 16   |

| Table 13: Interpolation rate                                | 17   |

| Table 14: Interpolation rate with extended IR divider       | 17   |

| Table 15: Maximum input frequency                           |      |

| Table 16: Sensor monitoring overview                        | 20   |

| Table 17: Recommended configuration for sensor monitoring   |      |

| Table 18: ABZ modes (Register CFG1)                         | 22   |

| Table 19: DSP mode                                          |      |

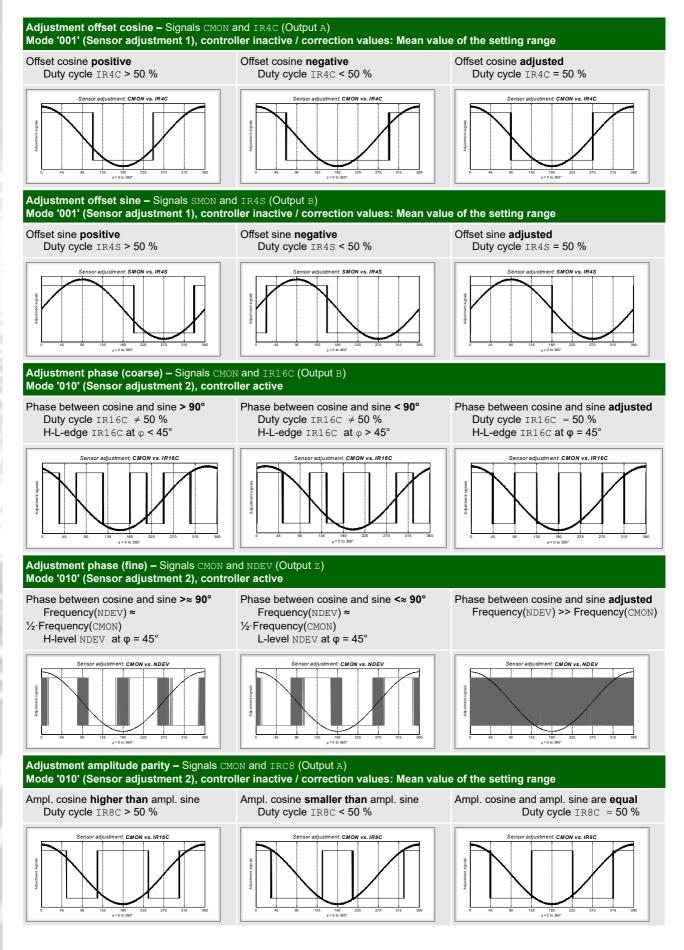

| Table 20: Sensor adjustment                                 |      |

| Table 21: Trigger mode/Reference point modes                | 25   |

| Table 22: Position registers                                |      |

| Table 23: Configuration of data format for positioning data |      |

| Table 24: Commands/Control signals                          | 27   |

| Table 25: SPI signals                                       | 28   |

| Table 26: SPI protocol                                      | 28   |

| Table 27: Register CFGSSI (SSI mode)                        |      |

| Table 28: EEPROM Addressing                                 |      |

| Table 29: Register overview                                 |      |

| Table 30: Absolute limit values                             |      |

| Table 31: Operating conditions                              |      |

| Table 32: Characteristic values clock/reset                 |      |

| Table 33: Characteristic values interpolation               |      |

| Table 34: Digital characteristic values                     |      |

| Table 35: Analogue characteristic values                    |      |

| Table 36: Characteristic values EEPROM                      |      |

| Table 37: Characteristic values SSI interface               |      |

| Table 38: IC connection voltages                            |      |

| Table 39: Connection of unused in- and outputs              | 45   |

|                                                             |      |

## 1 Overview

The interpolation circuit AM-IP4k serves to increase the resolution of incremental position and angular measuring systems with sinusoidal output signals offset by 90°. The input signals are subjected to an AMAC-specific internal gain and offset control, which automatically leads to a correction of amplitude and zero position. Additionally correction of concentricity errors as well as signal form errors are integrated. Furthermore the phase deviation of the input signals can be corrected statically via a digital potentiometer. By dividing the signal period up to 4096 times a position or angle value is calculated and then transferred to following components via a fast SPI interface, a SSI interface, or via standard ABZ square wave signals.

The interpolation circuit AM-IP4k is suitable for both input and output interfaces with 3.3V. It comprises three instrumentation amplifiers with adjustable gain factors. Sensors with voltage interface as well as measuring bridges can be connected directly to this interpolation IC. Sensors with current interface and photodiodearrays are adapted by a simple external circuit. The AM-IP4k can be used with both single-ended and differential signals. The noise of the sensor signals is reduced by a configurable low-pass filter. Additionally, a digital hysteresis can suppress the edge noise of the output signals at low input frequencies and at standstill. Thus, a consecutively connected interpolation counter works properly even in case of short-time disturbances. The quality of the signals issued by the sensors is monitored in the IC. For that purpose it is possible to activate 6 sources separately, which are producing an error signal.

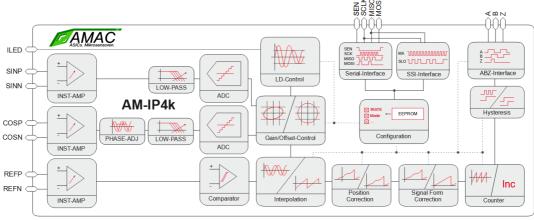

Figure 1: Block diagram

The integrated output signal interfaces (ABZ, SPI, SSI) and further features like an integrated multi-turn counter, the processing of distance coded reference marks, the possibilities of reference point adjustment and zero point adjustment and storage make the IC suitable for direct use in industrial control systems. Furthermore the IC can be used in absolute positioning measuring systems. For optical sensors a controlled current output is provided to control a laser diode. The IC's configuration depends on the specific application and is carried out via an internal EEPROM, configuration pins or serial interface (SPI).

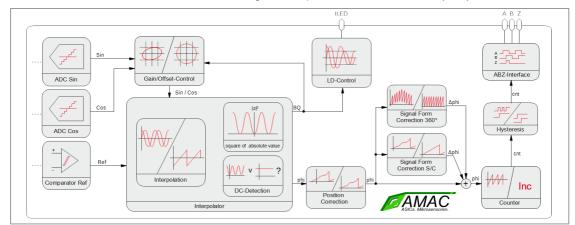

Figure 2: Functional block diagram

## 2 Features

| Interfaces                   |                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analogue input               | - Sine- / Cosine- / Reference signal: differential or single-ended<br>- Nominal amplitude configurable to 1 Vpp / 500 mVpp / 250 mVpp / 75 mVpp<br>- Maximum input frequency up to 220 kHz                                                                                                                                                                                                     |

| ABZ                          | - 90° square wave sequences (A/B/Z)<br>- Adjustable width of the index signal Z of ¼ or 1 period A/B<br>- Error signal<br>- Interrupt signal for μC<br>- Additional signals for sensor adjustment                                                                                                                                                                                              |

| SPI                          | <ul> <li>- 30 bit count value / 16 bit multi-turn value</li> <li>- Data rate up to 500,000 measured values/s</li> <li>- 9 bit signal monitoring</li> <li>- Compatible with standard SPI: 16 bit, MSB first, up to 25 MHz</li> <li>- Signal filter for noise suppression, configurable</li> </ul>                                                                                               |

| SSI                          | - SSI 20 bit or 32 bit<br>- 2 bit signal monitoring<br>- Gray code / binary code<br>- Adjustable timing<br>- SSI ring mode                                                                                                                                                                                                                                                                     |

|                              | - Trigger signal for measured value storage<br>- Zero signal and teach signal for sensor's zero point adjustment and storage                                                                                                                                                                                                                                                                   |

| Current output               | <ul> <li>Controlling a laser diode for optical sensors</li> <li>Controlled by square of the input signals' absolute value</li> <li>Set current adjustable in 256 steps</li> </ul>                                                                                                                                                                                                              |

| Configuration options        | - Internal EEPROM<br>- Serial SPI interface                                                                                                                                                                                                                                                                                                                                                    |

| Interpolation / Signal proce | ssing                                                                                                                                                                                                                                                                                                                                                                                          |

| Interpolation rates          | <ul> <li>Interpolation basis rate: 4096, 4000, 3200, 2560<sup>1)</sup></li> <li>Configurable divider: 1, 2, 4, 8, 16, 32, 64, 128 additionally for basic IR 4096 (256, 512, 1024)</li> <li>Interpolation rate adjustable at will via EEPROM table, default setting: 2560<sup>1)</sup></li> </ul>                                                                                               |

| Signal adjustment            | <ul> <li>AMAC-specific digital controller for the offset, control range ±10% of the nominal amplitude</li> <li>AMAC-specific digital controller for the amplitude, control range 60% 120% of the nominal amplitude</li> <li>Digital potentiometer with 64 steps for phase correction; setting range ±5° or ±10°</li> <li>Input signal monitoring with configurable error indication</li> </ul> |

| Signal correction            | <ul> <li>Wobble correction for periodic errors over 360° (rotary encoder)</li> <li>Signal form correction for periodic errors within one sine/cosine period (for linear encoder too)</li> <li>Can be activated or deactivated separately</li> </ul>                                                                                                                                            |

| Interference suppression     | - Adjustable low-pass filter (Cut-off frequencies 10 kHz, 75 kHz, 250 kHz)<br>- Digital hysteresis to suppress output edge noise<br>- Adjustable minimum edge separation (band width limitation) at the output                                                                                                                                                                                 |

| Reference signal processing  | <ul> <li>Adjustable reference position 0 360°</li> <li>Definition of the optimal reference position via SPI or additional signals</li> <li>Processing of distance coded reference marks</li> <li>Measured value trigger at the reference position</li> </ul>                                                                                                                                   |

| Other                        | <ul> <li>2-stage measured value trigger</li> <li>Programmable timer (3.2 μs 420 ms)</li> <li>Constant delay between sampling and measurement for all resolutions (at 40 MHz): without signal correction 2.35 μs; with signal correction 3.95 μs</li> <li>Multi-turn counter</li> </ul>                                                                                                         |

| Main features                |                                                                                                                                                                                                                                                                                                                                                                                                |

| Package                      | QFN56 (8 x 8 mm)                                                                                                                                                                                                                                                                                                                                                                               |

| Operating voltage            | 3.3 V                                                                                                                                                                                                                                                                                                                                                                                          |

| Temperature range            | -40 +125°C                                                                                                                                                                                                                                                                                                                                                                                     |

| Interface clock frequency    | SPI 25 MHz, SSI 5 MHz                                                                                                                                                                                                                                                                                                                                                                          |

## 3 Ordering information

| Product type       | Description                          | Article number |

|--------------------|--------------------------------------|----------------|

| AM-IP4k            | Interpolation circuit AM-IP4k, QFN56 | PR-50400-10    |

| USB to SPI Adapter | USB adapter for SPI interface        | PR-44025-10    |

Document: 50400-DB-1-3-E-IP4k\_AMAC

Features

## 4 Application overview

| Sinusoidal, vortage     Direct connection of AM-IP4k to sensor       Sinusoidal, current     Additional resistors required       Reference (index) track     Direct connection of AM-IP4k to sensor       Siguare wave     IC not suitable in principle       Signal specification (sensor)     Application of AM-IP4k to sensor       Sigmare mave     IC not suitable in principle       Signare mave     IC not suitable in principle       Sigmare mave     IC not suitable in principle       Sigmare maximum     Application of AM-IP4k to sensor       Som/w, nominal     Direct connection of AM-IP4k to sensor       Som/w, nominal     Direct connection of AM-IP4k to sensor       Sommanial     Direct connection of AM-IP4k to sensor       Single-ended, DC reference voltage     Direct connection of AM-IP4k to sensor       Single-ended, DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Float olicides 11 µA <sub>m</sub> 16 µA <sub>m</sub> Additional resistors required       Photo diodes 0.5 µA <sub>m</sub> Additional resistors required       Photo diodes 0.5 µA <sub>m</sub> Additional resistors required       Photo diodes 0.5 µA <sub>m</sub> Additional resistors required       Photo diodes 11 µA <sub>m</sub> 16 µA <sub>m</sub> Additional resistors required       Photo diodes 11 µA <sub>m</sub> 16 µA <sub>m</sub> Additional resistors required       Photo diodes 11 µA <sub>m</sub> 16 µA <sub>m</sub> Additional resistors required                                                                    | Signal form (Sensor)                         | Application of AM-IP4k                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|

| Sinusoidal, current     Additional resistors required       Reference (index) track     Direct connection of AM-IP4k to sensor       Square wave     IC not suitable in principle       Signal specification (sonsor)     Application of AM-IP4k       75mV <sub>10</sub> nominal     Direct connection of AM-IP4k to sensor       250mV <sub>20</sub> nominal     Direct connection of AM-IP4k to sensor       1 V <sub>20</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>20</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>20</sub> nominal     Direct connection of AM-IP4k to sensor       Single-ended, DC reference voltage     Direct connection of AM-IP4k to sensor       Single-ended, DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Single-ended, DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Photo diodes 05 µA,     Additional resistors required       Photo diodes 01 µA,16 µA,     Additional resistors required       Resistue measuring bridge (Magnetic sensors)     Direct connection of AM-IP4k to sensor       Fluctuating amplitude of the sensor     AM-IP4k contains a controller for amplitudes       O                                                                         |                                              |                                                                                                    |

| Reference (index) track     Direct connection of AM-IP4k to sensor       Square wave     IC not suitable in principle       Signal specification (sensor)     Application of AM-IP4k to sensor       250mV <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       250mV <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       20mV <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       30mV <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>in</sub> nominal     Direct connection of AM-IP4k to sensor       Single-ended, DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Single-ended, no DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Photo diodes 0.5 µA <sub>po</sub> Additional resistors required       Photo diodes 0.5 µA <sub>po</sub> Addit    |                                              |                                                                                                    |

| Square wave       IC not suitable in principle         Signal specification (sensor)       Application of AN-IP4k         75mV <sub>40</sub> nominal       Direct connection of AM-IP4k to sensor         500mV <sub>50</sub> nominal       Direct connection of AM-IP4k to sensor         500mV <sub>50</sub> nominal       Direct connection of AM-IP4k to sensor         2 V <sub>20</sub> nominal       Direct connection of AM-IP4k to sensor         2 V <sub>20</sub> nominal       Direct connection of AM-IP4k to sensor         Single-ended, no DC reference source inside sensor       Direct connection of AM-IP4k to sensor         Single-ended, no DC reference source inside sensor       Direct connection of AM-IP4k to sensor         Photo diodes 05 µA <sub>20</sub> Additional resistors required         Photo diodes 01 µA <sub>20</sub> 16 µA <sub>30</sub> AM-IP4k contains a controller for offsets         Photo diodes 01 µA <sub>20</sub> 16 µA <sub>30</sub> AM-IP4k contains a controller for offsets         Photo diodes 01 µA <sub>20</sub> 16 µA <sub>30</sub> AM-IP4k contains a controller for offsets         Phase at sensor not correctable       AM-IP4k contains a controller for offsets         Phase at sensor not correctable       AM-IP4k contains a controller for offsets <t< td=""><td></td><td></td></t<>    |                                              |                                                                                                    |

| Signal specification (sensor)         Application of AM-IP4k           75mV <sub>re</sub> nominal         Direct connection of AM-IP4k to sensor           250mV <sub>re</sub> nominal         Direct connection of AM-IP4k to sensor           20mminal         Direct connection of AM-IP4k to sensor           1 V <sub>en</sub> nominal         Direct connection of AM-IP4k to sensor           2 V <sub>en</sub> nominal         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor           Photo diodes 0.5 μA <sub>p</sub> Additional resistors required           Photo diodes 0.5 μA <sub>p</sub> Additional resistors required           Resistve measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for offsets           Phase at sensor not correctable         AM-IP4k provides the possibility for reference point adjustment           Variable reference signal position         AM-IP4k provides the possibility for reference point adjustment           Maximum signal frequency <td< td=""><td></td><td></td></td<> |                                              |                                                                                                    |

| 75mV <sub>ex</sub> nominal     Direct connection of AM-IP4k to sensor       250mV <sub>ex</sub> nominal     Direct connection of AM-IP4k to sensor       500mV <sub>ex</sub> nominal     Direct connection of AM-IP4k to sensor       1 V <sub>ex</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>ex</sub> nominal     Additional resistors required       Differential signal, DC reference voltage     Direct connection of AM-IP4k to sensor       Single-ended, no DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Single-ended, no DC reference source inside sensor     Direct connection of AM-IP4k to sensor       Photo diodes 0.5 µA <sub>xx</sub> Additional resistors required       Photo diodes 0.5 µA <sub>xx</sub> Additional resistors required       Resistive measuring bridge (Magnetic sensors)     Direct connection of AM-IP4k to sensor       Fluctuating amplitude of the sensor     AM-IP4k contains a controller for amplitudes       Offset at sensor not correctable     AM-IP4k contains a potentimeter for phase adjustment       Variable reference signal position     AM-IP4k contains a potentimeter for phase adjustment       Distance-coded reference marks     Special trigger mode for AM-IP4k when connected via SPI       Maximum Signal frequency     fma: = (vevolution / minute)-(signal periods / revolution) / 60       Linear encoders:     fma: = (vevolution / anti-) (signal period [in mm]) · 1000       fma: < 20 kHz                                                   |                                              |                                                                                                    |

| 250mV <sub>ve</sub> nominal     Direct connection of AM-IP4k to sensor       500mV <sub>ve</sub> nominal     Direct connection of AM-IP4k to sensor       1 V <sub>ve</sub> nominal     Direct connection of AM-IP4k to sensor       2 V <sub>ve</sub> nominal     Additional resistors required       Differential signal, DC reference voltage     Direct connection of AM-IP4k to sensor       Single-ended, DC reference source inside sensor     Direct connection of AM-IP4k to sensor or need for additional resistors required       Photo diodes 0.5 µA <sub>ve</sub> Additional resistors required       Resistive measuring bridge (Magnetic sensor)     Direct connection of AM-IP4k to sensor       Fluctuating amplitude of the sensor     AM-IP4k contains a controller for amplitudes       Offset at sensor not correctable     AM-IP4k contains a controller for affsets       Phase at sensor not correctable     AM-IP4k contains a potentiometer for phase adjustment       Variable reference signal position     AM-IP4k rovides the possibility for reference point adjustment       Distance-coder reference marks     Special trigger mode for AM-IP4k when connected via SPI       Maximum signal frequency     Image revolution / minute) (signal period [mm]) · 1000       I_max < 200 kHz                                                                                                                                                                                                                                                                 |                                              |                                                                                                    |

| 500mV <sub>re</sub> nominal         Direct connection of AM-IP4k to sensor           1 V <sub>a</sub> nominal         Direct connection of AM-IP4k to sensor           2 V <sub>a</sub> nominal         Additional resistors required           Differential signal, DC reference voltage         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor or need for additional resistors required           Photo diodes 0.5 μA <sub>80</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensor)         Direct connection of AM-IP4k to sensor           Photo diodes 11 μA <sub>80</sub> 16 μA <sub>90</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a potentimemeter for phase adjustment           Variable reference signal position         AM-IP4k contains a potentimemeter for phase adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         fmax = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fmax = (revolution rates up to 4096 via SPI/SSI           fmax < 40 MHz / Interpolation rate                            |                                              |                                                                                                    |

| Ngenominal         Direct connection of AM-IP4k to sensor           2 V <sub>ge</sub> nominal         Additional resistors required           Differential signal, DC reference voltage         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor or need for additional resistors required           Photo diodes 0.5 µA <sub>no</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensor)         Direct connection of AM-IP4k to sensor           Photo diodes 11 µA <sub>po</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensor)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a controller for amplitudes           Phase at sensor not correctable         AM-IP4k provides the possibility for reference point adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k we nonenceted via SPI           Maximum signal frequency         Maximum signal frequency           Rotary encoders:         fmax = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fmax = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fmax = (revolution / minute) (signal periods / revolution) /                         |                                              |                                                                                                    |

| 2 V <sub>to</sub> nominal       Additional resistors required         Differential signal, DC reference voltage       Direct connection of AM-IP4k to sensor         Single-ended, DC reference source inside sensor       Direct connection of AM-IP4k to sensor or need for additional resistors         Single-ended, DC reference source inside sensor       Direct connection of AM-IP4k to sensor or need for additional resistors         Photo diodes 0.5 µA <sub>pe</sub> Additional resistors required         Photo diodes 11 µA <sub>pp</sub> 16 µA <sub>pp</sub> Additional resistors required         Resistive measuring bridge (Magnetic sensors)       Direct connection of AM-IP4k to sensor         Fluctuating amplitude of the sensor       AM-IP4k contains a controller for onfisets         Phase at sensor not correctable       AM-IP4k contains a controller for phase adjustment         Variable reference signal position       AM-IP4k provides the possibility for reference point adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       Imax = (revolution / minute) (signal periods / revolution) / 60         Inear encoders:       fmax = (revolution / minute) (signal period [m mm]) · 1000         Imax < 40 MHz / Interpolation rate                                                                                                                                                                                                           |                                              |                                                                                                    |

| Differential signal, DC reference voltage         Direct connection of AM-IP4k to sensor           Single-ended, DC reference source inside sensor         Direct connection of AM-IP4k to sensor           Single-ended, no DC reference source inside sensor         Direct connection of AM-IP4k to sensor or need for additional resistors           Photo diodes 0.5 µA <sub>PP</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a controller for offsets           Phase at sensor not correctable         AM-IP4k contains a potentiometer for phase adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         Imms = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fms = (vwax [in m/s] / (signal periods / revolution) / 60           Linex < 40 MHz / Interpolation rate                                                                                                                                                                                                                                                                                                                                                                                  |                                              |                                                                                                    |

| Single-ended, DC reference source inside sensor       Direct connection of AM-IP4k to sensor         Single-ended, no DC reference source inside sensor       Direct connection of AM-IP4k to sensor on end for additional resistor         Photo diodes 0.5 µA <sub>po</sub> Additional resistors required         Photo diodes 0.5 µA <sub>po</sub> Additional resistors required         Resistive measuring bridge (Magnetic sensors)       Direct connection of AM-IP4k to sensor         Fluctuating amplitude of the sensor       AM-IP4k contains a controller for amplitudes         Offset at sensor not correctable       AM-IP4k contains a controller for affsets         Phase at sensor not correctable       AM-IP4k contains a controller for phase adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       Image (revolution / minute)-(signal periods / revolution) / 60         Linear encoders:       fmax = (revolution rates up to 4096 via SPI/SSI         Maximum counter frequency at ABZ is known       Adjustment of AM-IP4k possible via CFGTPP         Subsequent electronics       Output to pController/DSP/PFQA         Output to industrial control       Connection via SPI interface         Output to industrial control       Connection via SI or ABZ interface         System contains several channels       Simultaneous use at a single SPI/SSI bus possible         Real-tim                                                                 |                                              |                                                                                                    |

| Single-ended, no DC reference source inside sensor       Direct connection of AM-IP4k to sensor or need for additional resistor         Photo diodes 0.5 µA <sub>pp</sub> Additional resistors required         Photo diodes 11 µA <sub>pp</sub> 16 µA <sub>pp</sub> Additional resistors required         Resistive measuring bridge (Magnetic sensors)       Direct connection of AM-IP4k to sensor         Fluctuating amplitude of the sensor       AM-IP4k contains a controller for amplitudes         Offset at sensor not correctable       AM-IP4k contains a potentiometer for phase adjustment         Variable reference signal position       AM-IP4k contains a potentiometer for phase adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       fmmx = (revolution / minute)-(signal periods / revolution) / 60         Linear encoders:       fmmx = (revolution rates up to 4096 via SPI/SSI         fmx< < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |                                                                                                    |

| Photo diodes 0.5 μA <sub>PP</sub> Additional resistors required           Photo diodes 0.5 μA <sub>PP</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a controller for amplitudes           Phase at sensor not correctable         AM-IP4k contains a controller for phase adjustment           Variable reference signal position         AM-IP4k provides the possibility for reference point adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         Rotary encoders:         fmax = (revolution / minute)-(signal periods / revolution) / 60           fmax < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                            |                                                                                                    |

| Photo diodes 11 μA <sub>sp</sub> 16 μA <sub>sp</sub> Additional resistors required           Resistive measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a controller for offsets           Phase at sensor not correctable         AM-IP4k contains a potentiometer for phase adjustment           Variable reference signal position         AM-IP4k provides the possibility for reference point adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         Integrating and trequency           Rotary encoders:         fmax = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fmax = (revolution rates up to 4096 via SPI/SSI           Maximum counter frequency at ABZ is known         Adjustment of AM-IP4k possible via CFGTPP           Subsequent electronics         Output to μController/DSP/FPGA           Output to uController/DSP/FPGA         Connection via SPI interface           Output to industrial control         Connection via SPI interface           Output to industrial control         Connection via SPI interface           Output to industrial control         Connection via SPI interface           Output to industrial contro                                                        | -                                            |                                                                                                    |

| Resistive measuring bridge (Magnetic sensors)         Direct connection of AM-IP4k to sensor           Fluctuating amplitude of the sensor         AM-IP4k contains a controller for amplitudes           Offset at sensor not correctable         AM-IP4k contains a controller for offsets           Phase at sensor not correctable         AM-IP4k contains a potentiometer for phase adjustment           Variable reference signal position         AM-IP4k provides the possibility for reference point adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         Maximum signal frequency           Rotary encoders:         fmax = (revolution / minute) (signal periods / revolution) / 60           Linear encoders:         fmax = (revolution / minute) (signal periods / revolution) / 60           fmax < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • •                                          | · · ·                                                                                              |

| Fluctuating amplitude of the sensor       AM-IP4k contains a controller for amplitudes         Offset at sensor not correctable       AM-IP4k contains a controller for offsets         Phase at sensor not correctable       AM-IP4k contains a potentiometer for phase adjustment         Variable reference signal position       AM-IP4k provides the possibility for reference point adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       Rotary encoders:       f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              | · · · ·                                                                                            |

| Offset at sensor not correctable       AM-IP4k contains a controller for offsets         Phase at sensor not correctable       AM-IP4k contains a potentiometer for phase adjustment         Variable reference signal position       AM-IP4k provides the possibility for reference point adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |                                                                                                    |

| Phase at sensor not correctable         AM-IP4k contains a potentiometer for phase adjustment           Variable reference signal position         AM-IP4k provides the possibility for reference point adjustment           Distance-coded reference marks         Special trigger mode for AM-IP4k when connected via SPI           Maximum signal frequency         Imax = (revolution / minute)-(signal periods / revolution) / 60           Linear encoders:         fmax = (revolution / minute)-(signal periods / revolution) / 60           Linear encoders:         fmax = (vMax [in m/s] / (signal period [in mm]) · 1000           fmax < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              | · · ·                                                                                              |

| Variable reference signal position       AM-IP4k provides the possibility for reference point adjustment         Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       Rotary encoders:         Innax < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |                                                                                                    |

| Distance-coded reference marks       Special trigger mode for AM-IP4k when connected via SPI         Maximum signal frequency       Rotary encoders:       f_max = (revolution / minute) (signal periods / revolution) / 60         Linear encoders:       f_max = (revolution / minute) (signal periods / revolution) / 60         Interpolation rates:       f_max = (revolution / minute) (signal periods / revolution) / 60         Maximum counders:       f_max = (revolution / minute) (signal periods / revolution) / 60         Maximum counter frequency at ABZ is known       All interpolation rates up to 4096 via SPI/SSI         Maximum counter frequency at ABZ is known       Adjustment of AM-IP4k possible via CFGTPP         Subsequent electronics       Connection via SPI interface         Output to µController/DSP/FPGA       Connection via SSI or ABZ interface         Output to industrial control       Connection via SSI or ABZ interface         Output to industrial control       Constant delay of 2.4 µs (4.0 µs with activated signal correction), utrigger or timer         IC configuration       Internal EEPROM, all registers configurable via SPI         Signal specification LVCMOS       Inputs/Outputs can be used directly         Signal specification RS-422       Line driver required         Limited size       QFN56, outer dimensions 8 mm x 8 mm         Minimum circuit       See figure 21<br>• 8 Block-C<br>• 3 pull-up resistors (NRES, NERR, MISO) </td <td></td> <td></td>                                             |                                              |                                                                                                    |

| Maximum signal frequency         Rotary encoders:       fmax = (revolution / minute)·(signal periods / revolution) / 60         Linear encoders:       fmax = (v <sub>MAX</sub> [in m/s] / (signal period [in mm]) · 1000         fmax       420 kHz         All interpolation rates up to 4096 via SPI/SSI         fmax       For use of the ABZ output         Maximum counter frequency at ABZ is known       Adjustment of AM-IP4k possible via CFGTPP         Subsequent electronics       Connection via SPI interface         Output to µController/DSP/FPGA       Connection via SI or ABZ interface         Output to industrial control       Connection via SSI or ABZ interface         System contains several channels       Simultaneous use at a single SPI/SSI bus possible         Real-time application / Equidistant sampling       Constant delay of 2.4 µs (4.0 µs with activated signal correction), u         If configuration       Internal EEPROM, all registers configurable via SPI         Signal specification LVCMOS       Inputs/Outputs can be used directly         Signal specification RS-422       Line driver required         Limited size       Package         QEN56, outer dimensions 8 mm x 8 mm       See figure 21         • 8 Block-C       • 3 pull-up resistors (NRES, NERR, MISO)                                                                                                                                                                                                                                                     | • •                                          |                                                                                                    |

| Rotary encoders:       f <sub>max</sub> = (revolution / minute)-(signal periods / revolution) / 60         Linear encoders:       f <sub>max</sub> = (v <sub>MAX</sub> [in m/s] / (signal period [in mm]) · 1000         f <sub>max</sub> < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              | Special trigger mode for AM-IP4k when connected via SPI                                            |

| Linear encoders:       fmax = (VMAX [in m/s] / (signal period [in mm]) · 1000         fmax < 220 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |                                                                                                    |

| fmax < 220 kHzAll interpolation rates up to 4096 via SPI/SSIfmax < 40 MHz / Interpolation rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |                                                                                                    |